A

TC白菜网总站(广州)工程有限公司的SiC MOSFET栅极电压规范(+20V/-5V)是严格根据JEDEC来做的认证,保证产品在室温下工作寿命不小于10年。对于超出栅极电压规范的应用情况,主要有以下两个方面的考量。

第一,栅极本身的寿命模型主要由SiO2的TDDB(Time Dependent Dielectric Breakdown 时间依赖的介质击穿)模型来确定,已经有大量的数据表明SiC上生长的SiO2介质层的质量跟Si上生长的SiO2是一样优良的,所以从TDDB的角度来看,20V的栅介质所能承受的更高电压以及在该电压下的寿命模型跟Si MOSFET和IGBT是一致的;TC白菜网总站(广州)工程有限公司正在用瞻芯自己的SiC MOSFET建立SiO2栅介质工艺和器件的寿命模型。

第二,SiC MOSFET跟Si MOS产品(MOSFET和IGBT)最大的差别和挑战就在于PBTI(Positive Bias Temperature Instability正偏压温度不稳定性)和NBTI(Negative Bias Temperature Instability负偏压温度不稳定性),加正偏压后器件Vth会增加,加负偏压后器件Vth会减小;在JEDEC认证条件下,在栅极电压规范内工作,器件的寿命是可以得到保证的;对于超出栅压规范的应用寿命模型,TC白菜网总站(广州)工程有限公司正在搭建设备并且做详细规划和研究;总体说来,只要正栅压不超过25V,负栅压不低于-10V,Duty Cycle比较小的脉冲不会对器件造成性能的不可恢复性损伤,具体的定量关系和寿命模型会在第一轮研究结束时给出。

A

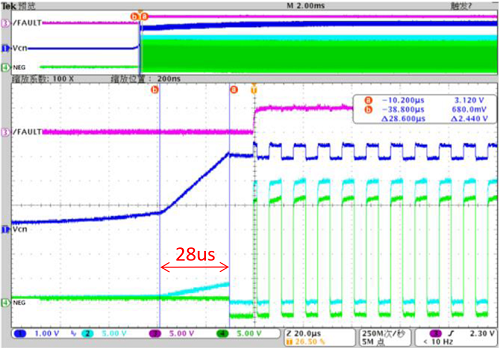

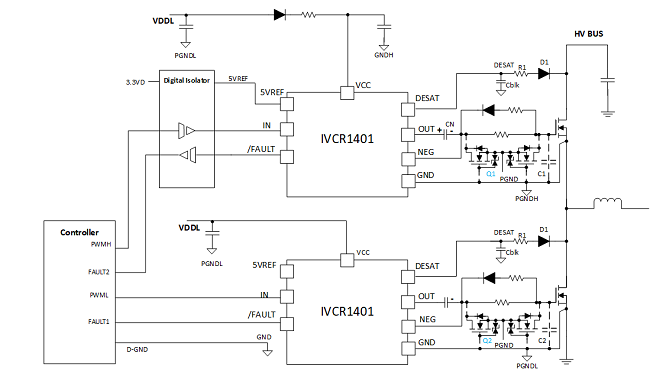

瞻芯开发了工业界首款采用8引脚封装,集成负压驱动的35V/4A驱动器IVCR1401D/IVCR1404DP. 在驱动器启动后,NEG输出被拉至GND,内部的电流源快速为负压电容充电,负压建立后,NEG引脚被释放,内部的负压调节器可将负压调节至-3.5V以正常运行,之后,栅极驱动信号NEG在(VCC-3.5V)和-3.5之间进行切换,如下图所示为负压电容的负压建立过程,1uF电容充电大约需要28us。

应使用超过100倍Cg电容的X7R电容,来减小负压电容上的纹波,使负压可靠稳定的建立运行并进行驱动。在我司的老化测试系统电路已经使用该芯片进行过验证,在1000V/20A/125℃的运行条件下驱动SiC MOSFET,连续运行1000h后,仍然能够稳定可靠的进行驱动。

A

SiC MOSFET相比于传统的Si功率器件具有更快的开关速度,然而这种快速的暂态过程会使SiC MOSFET的开关性能对回路的寄生参数更加敏感,尤其体现在驱动波形上。

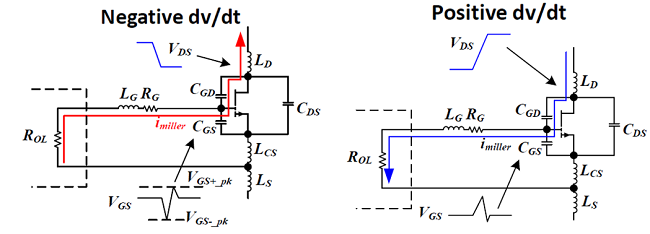

如下图所示为米勒效应产生的电压尖峰。在SiC MOSFET的半桥应用中,下管保持关断状态,上管关断时,会产生较大的dv/dt,由于功率回路和驱动回路中的寄生电感,会产生一个较大的米勒电流,该电流会在驱动电阻RG上产生一个压降,从而导致在VGS波形上出现一个负尖峰;同理,当上管导通时,也会产生较大的dv/dt,由于回路中存在的寄生电感,也会产生一个较大的米勒电流,该电流会在驱动电阻RG上产生一个压降,从而导致在VGS波形上出现一个正尖峰。

米勒效应产生的电压负尖峰 米勒效应产生的电压正尖峰

为了减少驱动的负压尖峰,有以下几个方面的建议:

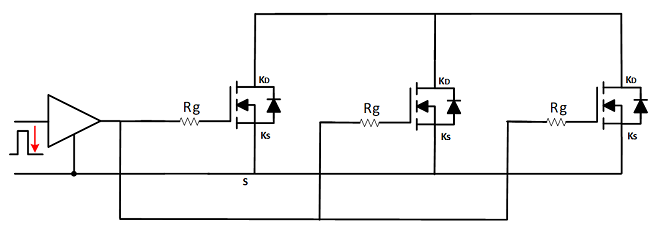

1) 在驱动电阻RG上并联一个back-to-back MOS,来降低米勒效应在RG上产生的压降,从而减小米勒尖峰电压,如下图中的Q1、Q2;

2) 将驱动芯片尽可能靠近SiC MOSFET的栅极,尽可能减小驱动回路中的寄生电感;

3) 在Layout上尽量减小功率回路的面积,尽可能减小功率回路和驱动回路中的共源极电感;

4) 在条件允许的情况下,使用TO247-4封装的SiC MOSFET,尽可能采用Kelvin驱动以减少器件引脚所带来的寄生电感。

A

SiC MOSFET振荡问题最关键的是首先要解决驱动回路振荡问题,防止因为驱动信号振荡而导致的振荡。为了解决驱动回路振荡,需要将驱动芯片尽可能靠近SiC MOSFET的栅极,尽可能减小寄生电感,减少振荡。

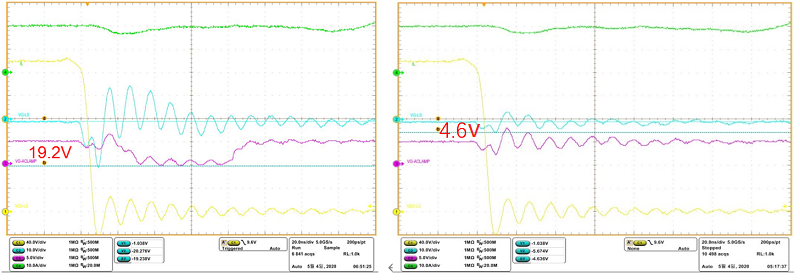

下面两张图,上图为驱动芯片离SiC MOSFET比较远的测试波形,下图为离的比较近的测试波形。两图中天蓝色波形为Vgs波形,黄色为Vds波形。 左图中米勒尖峰高达19.2V,右图的米勒尖峰只有4.6V,改善这么大的主要原因就是驱动IC离SiC MOSFET比较近。

驱动IC离MOSFET比较远的测试波形 驱动IC离MOSFET比较近的测试形

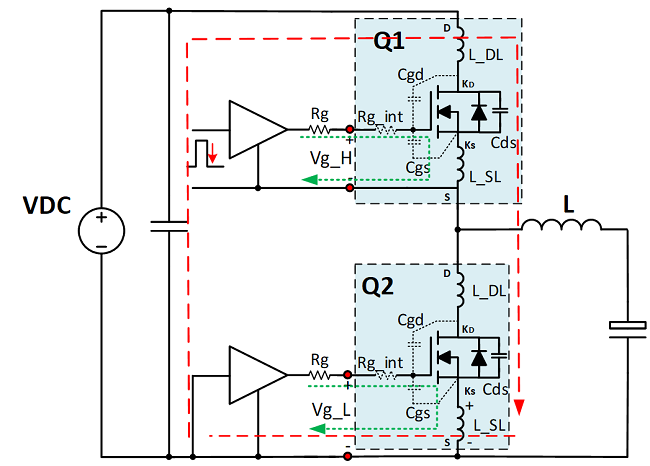

下面再说明一下SiC MOSFET的Layout的一些注意点,良好的Layout有助于减小振荡。首先驱动IC尽量离SiC MOSFET越近越好,以保证驱动回路面积越小越好。其次, 高频振荡是由PCB 和MOSFET的杂散电感杂散电容(主要是Coss)之间的振荡引起。如下图中,红色的虚线是功率回路的面积,绿色的虚线是驱动回路面积。这些面积越小则SiC MOSFET开关时的振荡越小。

A

不能沿用。因为采用驱动板的方式,驱动回路寄生电感比较大,从而需要更大的驱动电阻来阻尼,进而导致开关速度变慢,损耗增大。如果不用更大的驱动电阻来阻尼,那么Vgs波形会导致比较大的振荡,进而导致Vds振荡,从而增加开关损耗。另,寄生电感比较大本身就增加了驱动回路阻抗,驱动电路的抗米勒能力减弱,导致开关速度变慢,损耗也增大。

A

要保证每个SiC MOSFET的驱动回路和主功率回路尽量对称,要求驱动芯片输出到每个SiC MOSFET的栅极距离全部一样,每个SiC MOSFET需要单独的Rg来增加一致性,如果并联的MOSFET共用一个驱动电阻将会导致阈值电压最小的那个MOSFET最先开通,同时会将其他的MOSFET的Vgs钳位在该阈值电压下,从而导致只是阈值电压最小的MOSFET开通,其余所有的管子全部未开通。关断过程也是如此,阈值电压最高的那个MOSFET先关闭,同时将电压钳位在该阈值电压下,直到该管完成关断过程。由此可见,使用一个驱动电阻来驱动所有的MOSFET会造成比较大的开关瞬间的动态不均流。为此需要为每个MOSFET配置单独的Rg,从而使得每个MOSFET的Vgs解耦,增强动态均流。静态的均流特性主要靠MOSFET本身的参数一致性来实现,需要仔细挑选参数一致的MOSFET来做直接并联。